# **Языки описания схем**

[mk.cs.msu.ru](http://mk.cs.msu.ru) → Лекционные курсы → Языки описания схем

## Блок 9

Последовательные схемы

Лектор:

**Подымов Владислав Васильевич**

E-mail:

**valdus@yandex.ru**

ВМК МГУ, 2024/2025, осенний семестр

# Последовательные схемы

Последовательная схема, или **схема с памятью**, — это цифровая схема, выходные значения которой существенно зависят от входных значений в предыдущие моменты времени (а не только в текущий момент, как в комбинационной схеме)

Триггеры — это простые примеры последовательных схем

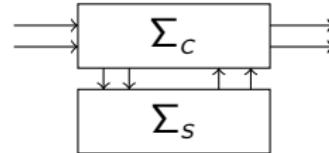

Типичное устройство последовательной схемы  $\Sigma$ :

$\Sigma_s$  — последовательная часть: набор триггеров

$\Sigma_c$  — комбинационная часть: комбинационная схема

Входы  $\Sigma$  и выходы  $\Sigma_s$  направляются на входы  $\Sigma_c$

Выходы  $\Sigma_c$  направляются на выходы  $\Sigma$  и входы  $\Sigma_s$

# Последовательные схемы

Состоянием схемы называется

совокупность состояний триггеров последовательной части

Последовательная схема называется **синхронной**, если

- ▶ в ней содержится тактовый сигнал с заданным активным уровнем и

- ▶ её состояние может изменяться

**только** во время передних фронтов тактового сигнала

Остальные схемы принято называть **асинхронными**

**Исключение:** если в схеме содержится сигнал **асинхронного сброса**, пересылаемый на соответствующие входы всех триггеров последовательной части, то схема также может считаться синхронной

За исключением нескольких особых случаев,

в курсе будут рассматриваться **только** синхронные схемы:

- ▶ На практике основная масса цифровых микросхем синхронна

- ▶ Разработка нетривиальных асинхронных микросхем —

это трудно и требует дополнительных специальных знаний

## Последовательные схемы

Как правило, в последовательной части синхронной схемы содержатся **только** синхронные триггеры, на тактовые входы которых посыпается тактовый сигнал схемы

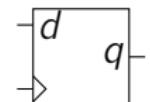

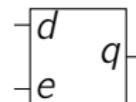

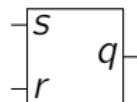

Некоторые понятия и обозначения напрямую переносятся с триггеров на последовательные схемы:

- ▶ Тактовый вход: *clk*, ▷

- ▶ Синхронный сброс: *sr*

- ▶ Асинхронный сброс: *ar*

По умолчанию в изображениях последовательных схем принято не рисовать (опускать) соединения для упомянутых входов триггеров последовательной части схемы: считается, что эти входы соединены с соответствующими входами схемы

# Последовательные схемы

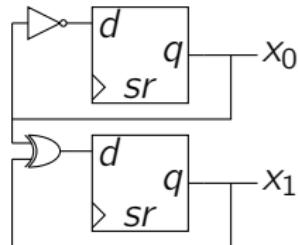

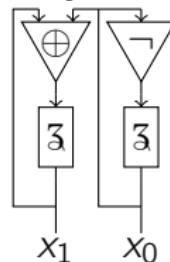

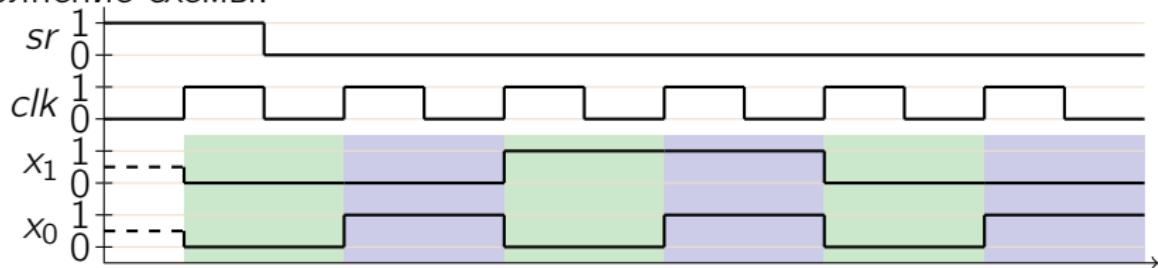

Пример:

Соответствующая СФЭЗ:

Выполнение схемы:

Это двухбитовый счётчик:

на выходах ( $x_1x_0$ ) последовательно в цикле

выставляются двоичные записи чисел 0, 1, 2, 3