# Языки описания схем

[mk.cs.msu.ru](http://mk.cs.msu.ru) → Лекционные курсы → Языки описания схем

## Блок П5

Практика:

операционный и управляющий автоматы

в Verilog

Лектор:

**Подымов Владислав Васильевич**

E-mail:

**valdus@yandex.ru**

ВМК МГУ, 2024/2025, осенний семестр

## Упражнение

Разработать на языке Verilog

синхронную схему с асинхронным сбросом с заданным поведением,

придерживаясь принципа разделения данных и управления:

- ▶ Разработать операционный автомат

- ▶ Разработать управляющий автомат

как комбинационную схему или типовую реализацию автомата

- ▶ Соединить операционный и управляющий автоматы

в итоговую схему

# Упражнение

## 1. Счётчик

выход ширины 8:  $y$

- ▶  $y(1) = 0$

- ▶  $y(t + 1) = y(t) + 1$  (*с переполнением*)

## 2. Двойной чередующийся счётчик

выходы ширины 8:  $y, z$

- ▶  $y(1) = z(1) = 0$

- ▶ После сброса

значения счётчиков (*по тактам*) поочерёдно увеличиваются на 1:

сначала  $y$ , затем  $z$ , затем  $y$ , затем  $z$ , ...

## 3. Двойной конечный счётчик

выходы ширины 8:  $y, z$

- ▶  $y(1) = z(1) = 0$

- ▶ После сброса

значение  $y$  два раза увеличивается на 1,

затем значение  $z$  три раза увеличивается на 1,

и затем значения не изменяются

# Упражнение

## 4. Двойной счётчик с управляемым сбросом

входы ширины 1:  $r, n$

выходы ширины 8:  $y_0, y_1$

►  $y_0(1) = y_1(1) = 0$

► После сброса:

► Если  $r(t) = 0$ , то  $y_0(t+1) = y_0(t) + 1$  и  $y_1(t+1) = y_1(t) + 1$

► Если  $r(t) = 1$ , то  $y_{n(t)}(t+1) = 0$  и  $y_{1-n(t)}(t+1) = y_{1-n(t)}(t) + 1$

## 5. Двойной ограниченный счётчик с управляемым сбросом

входы ► ширины 1:  $r, n$

► ширины 8:  $bound$

выходы ширины 8:  $y_0, y_1$

► *Отличие от предыдущего пункта:*

если  $y_i(t) = bound(t)$  и значение  $y_i$  должно увеличиться на 1,

то вместо увеличения это значение остаётся прежним ( $i \in \{0, 1\}$ )

# Упражнение

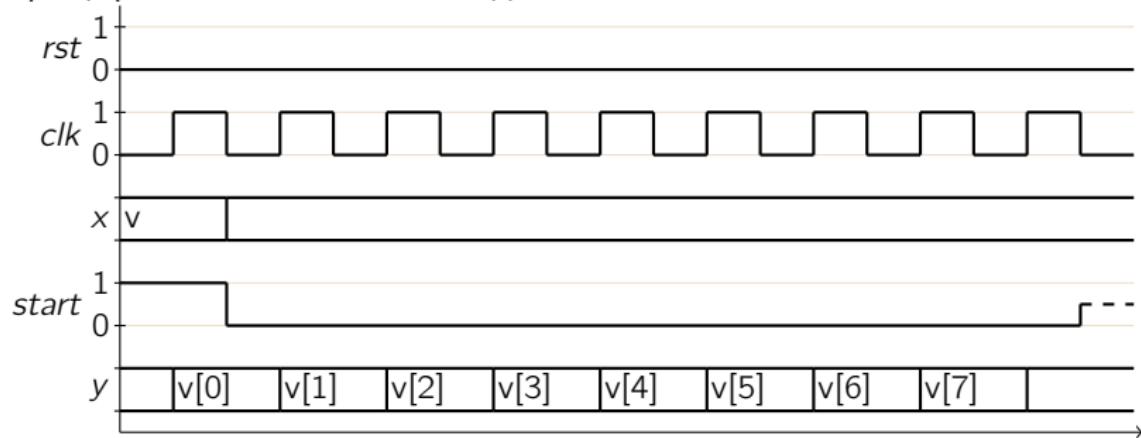

## 6. Сериализатор (база)

- входы ► ширины 8:  $x$

► ширины 1:  $start$

выход ширины 1:  $y$

Специфицированная часть поведения:

## Упражнение

### 7. Сериализатор (индикатор последнего разряда)

входы ► ширины 8:  $x$

► ширины 1:  $start$

выход ширины 1:  $y$ ,  $msb$

► *Новое в поведении:*  $msb = 1 \Leftrightarrow$  в  $y$  выдаётся значение  $v[7]$

### 8. Сериализатор (управление сменой разрядов)

входы ► ширины 8:  $x$

► ширины 1:  $start$ ,  $next$

выход ширины 1:  $y$ ,  $msb$

► *Новое в поведении:*

*если* на текущем такте в  $y$  выдаётся значение  $v[i]$

и в конце такта читается значение  $next = 0$ ,

*то* выдача следующих значений (или конец выдачи, если  $i = 7$ )

откладывается на один такт,

и на следующем такте выдаётся значение  $v[i]$

# Упражнение

## 9. Сериализатор (замедление)

- входы ► ширины 8:  $x$

► ширины 1:  $start$

выход ширины 1:  $y$ ,  $msb$

- *Новое в поведении:*

каждый разряд  $v[i]$  выдаётся в у три такта подряд вместо одного, после чего (без откладываний) выдаются следующие разряды

## 10. Сериализатор (индикатор конца)

- входы ► ширины 8:  $x$

► ширины 1:  $start$

выход ширины 1:  $y$ ,  $finish$

- *Новое в поведении:*

$finish = 1 \Leftrightarrow$  сейчас третий такт выдачи значения  $v[7]$