# Математические модели и методы логического синтеза СБИС

Осень 2015

# План семинара

- Основные типы логических схем с памятью (зашелки и регистры).

- Зашелка на основе мультиплексора

- D-триггер

- RS-триггер

- Лабораторная работа – проектирование логических схем с памятью.

# Защелки и регистры

- Защелка (latch) – чувствительный к уровню сигнала схема с памятью

- Регистр (register) – управляемая фронтом сигнала схема с памятью

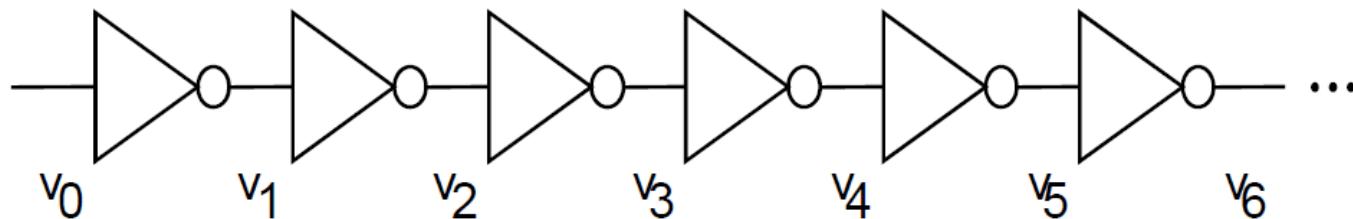

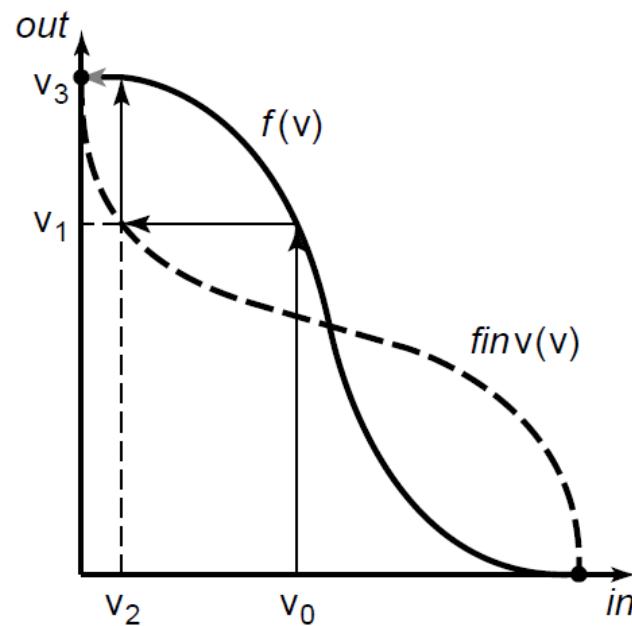

# Принцип бистабильности

- Цепочка инверторов

- Два стабильных состояния

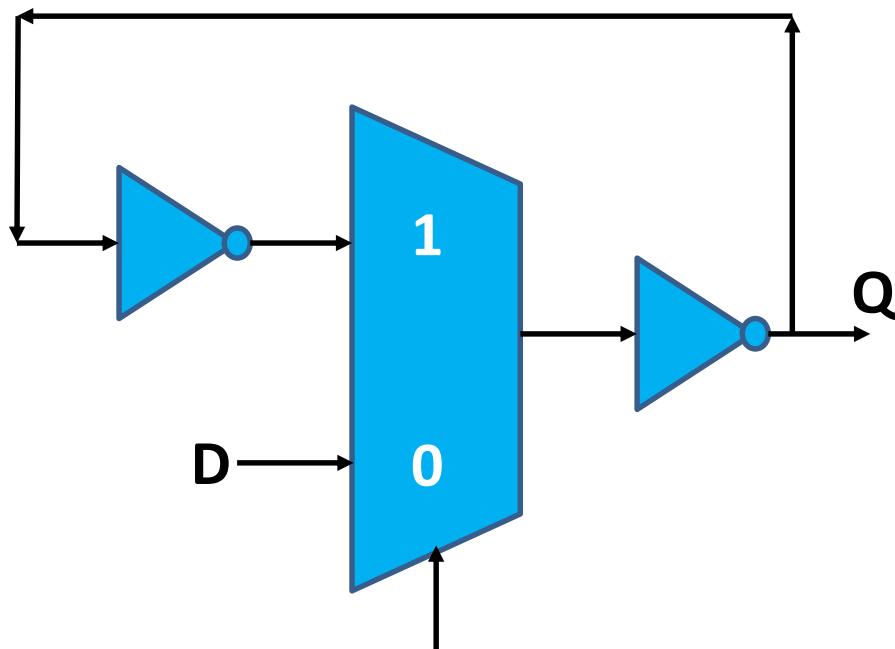

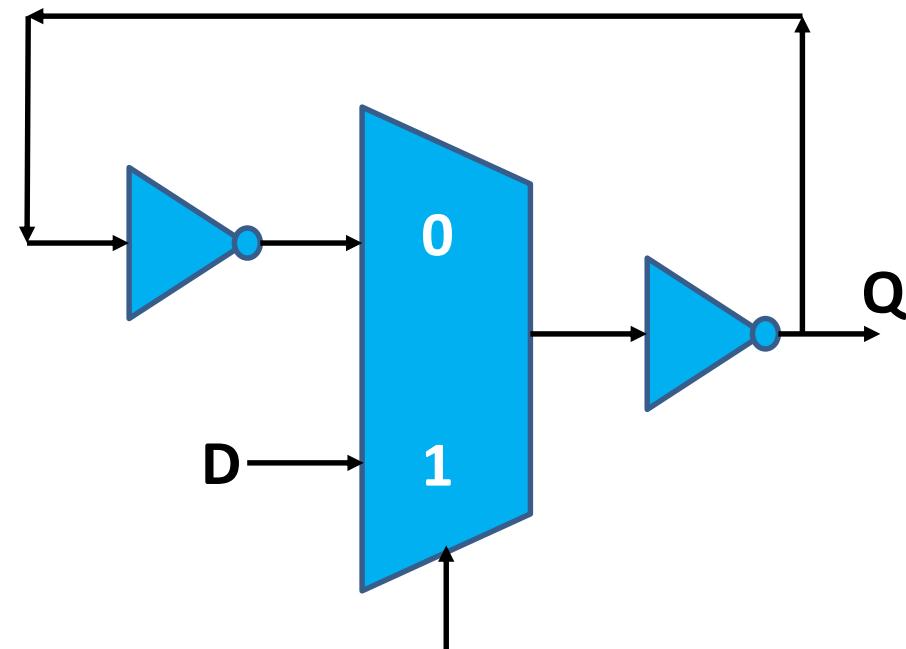

# Защелки, основанные на мультиплексоре

Отрицательная

защелка

Синхронизирующий

сигнал

Положительная

защелка

Синхронизирующий

сигнал

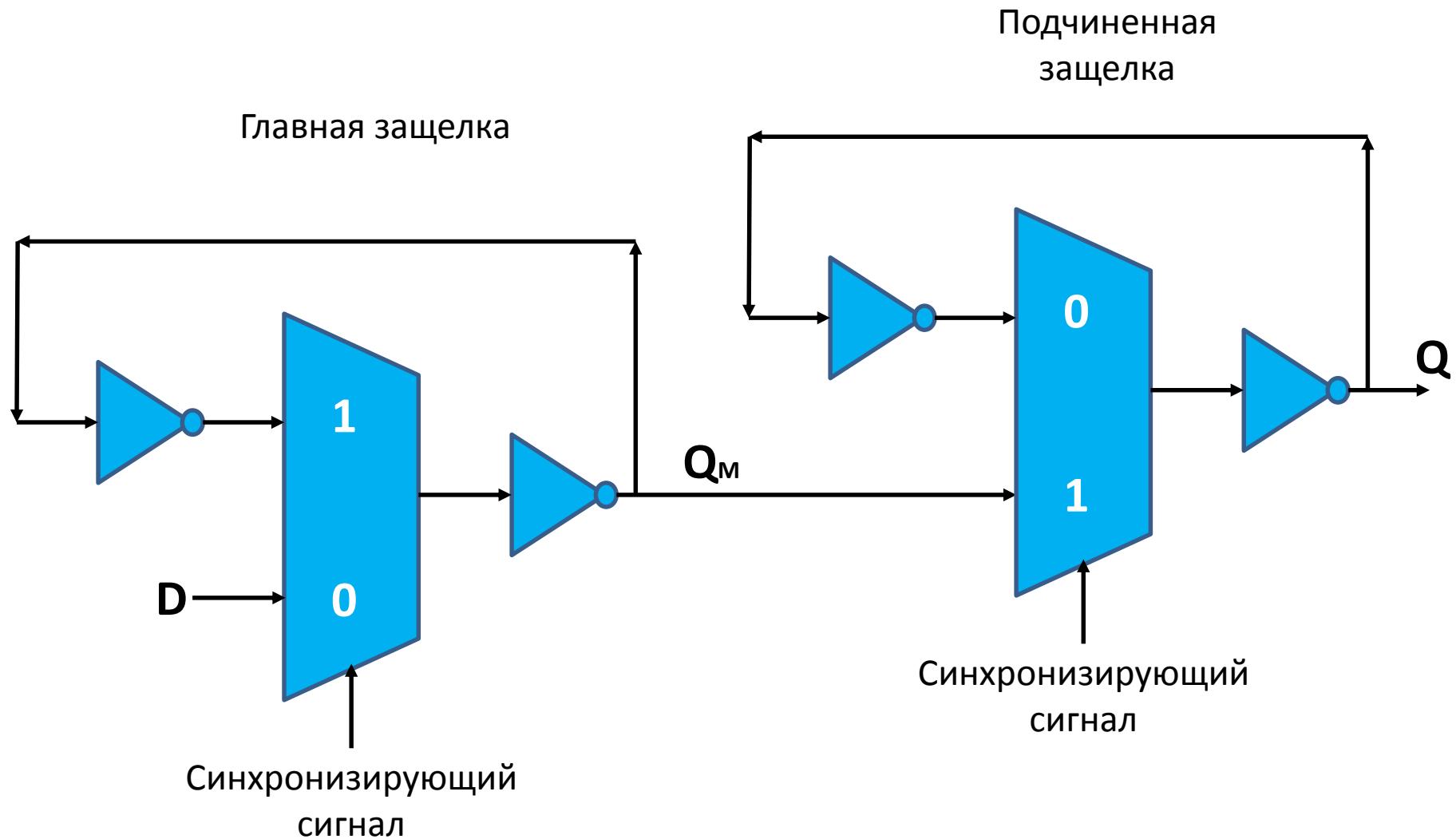

# Логическая схема D-триггера

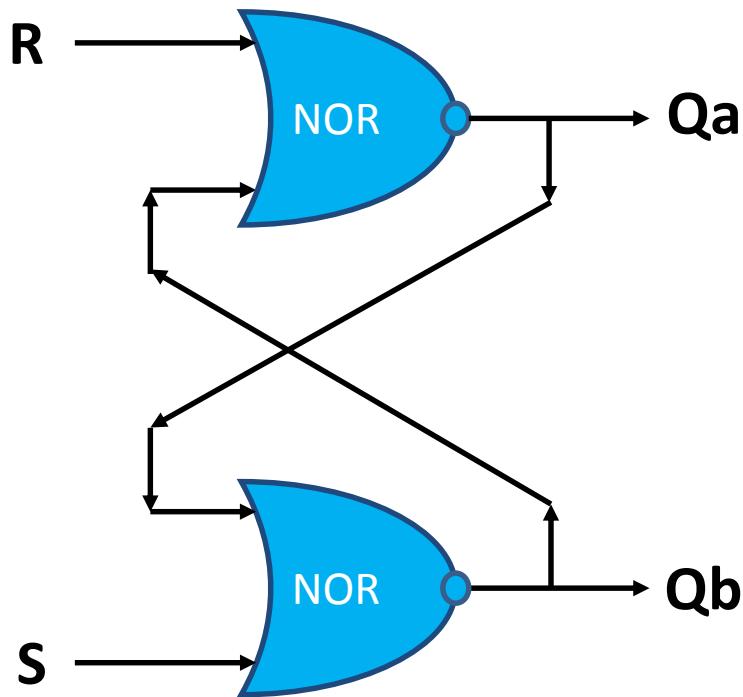

# RS-триггер (защелка) – запись данных методом грубой силы

| S | R | $Q_a$ | $Q_b$ |

|---|---|-------|-------|

| 0 | 0 | *     | *     |

| 0 | 1 | 1     | 0     |

| 1 | 0 | 0     | 1     |

| 1 | 1 | 0     | 0     |