# Языки описания схем

(mk.cs.msu.ru o Лекционные курсы o Языки описания схем)

#### Блок ПЗ

Лектор:

Практика: Подымов Владислав Васильевич Verilog и процедуры

E-mail:

valdus@yandex.ru

- Разработать модуль с заданным поведением в поддерживаемом фрагменте синтаксиса языка Verilog

- Выполнить программную симуляцию модуля с перебором всевозможных наборов булевых значений на входах

- 1. Демультиплексор с двумя однобитовыми выходами

```

входы ширины 1: x, s

выходы ширины 1: y_0, y_1:

\triangleright y_s = x

```

- $v_{1-s} = 0$

- 2. Демультиплексор с двумя двухбитовыми выходами

- ВХОДЫ ▶ ширины 2: х

- ▶ ширины 1: s

выходы ширины 2:  $y_0$ ,  $y_1$ :

- $y_s = x$

- $v_{1-s} = 0$

- Разработать модуль с заданным поведением в поддерживаемом фрагменте синтаксиса языка Verilog

- Выполнить программную симуляцию модуля с перебором всевозможных наборов булевых значений на входах

3. Демультиплексор с четырьмя однобитовыми выходами, собранными в шину

- ВХОДЫ ▶ ширины 1: х

- ▶ ширины 2: s

выход ширины 4: у:

- $\triangleright$  s-й разряд выхода y равен x

- значение в остальных разрядах 0

- Разработать модуль с заданным поведением

в поддерживаемом фрагменте синтаксиса языка Verilog

- ▶ Выполнить программную симуляцию модуля с перебором всевозможных наборов булевых значений на входах

- 4. Простое двухразрядное арифметическое устройство

```

входы ▶ ширины 2: x, y▶ ширины 1: sвыход ширины 4: z:

```

- если s = 0, то z = x + y

- ightharpoonup если s=1, то  $z=x\cdot y$

- 5. Простое трёхразрядное арифметическое устройство

```

входы \blacktriangleright ширины 3: x, y \blacktriangleright ширины 1: s выход ширины 6: z: \blacktriangleright если s=0, то z=x+y

```

- если s = 0, то z = x + y

- ightharpoonup если s=1, то  $z=x\cdot y$

- Разработать модуль с заданным поведением

в поддерживаемом фрагменте синтаксиса языка Verilog

- Выполнить программную симуляцию модуля для заданного сценария выполнения

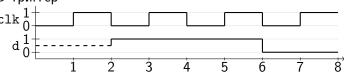

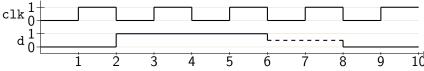

1. D-триггер

2. Параллельный регистр ширины 4

- Разработать модуль с заданным поведением

в поддерживаемом фрагменте синтаксиса языка Verilog

- Выполнить программную симуляцию модуля для заданного сценария выполнения

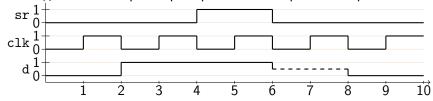

- 3. D-триггер с синхронным сбросом

4. Параллельный регистр ширины 4 с синхронным сбросом

- Разработать модуль с заданным поведением

в поддерживаемом фрагменте синтаксиса языка Verilog

- Выполнить программную симуляцию модуля для заданного сценария выполнения

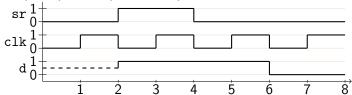

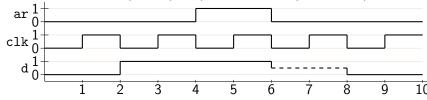

- 5. D-триггер с асинхронным сбросом

6. Параллельный регистр ширины 4 с асинхронным сбросом

- Разработать модуль с заданным поведением

в поддерживаемом фрагменте синтаксиса языка Verilog

- Выполнить программную симуляцию модуля для заданного сценария выполнения

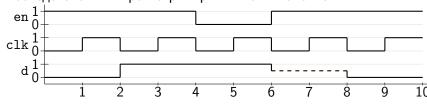

- 7. D-триггер с включением

8. Параллельный регистр ширины 4 с включением

- Разработать модуль с заданным поведением

в поддерживаемом фрагменте синтаксиса языка Verilog

- ▶ Выполнить программную симуляцию модуля для заданного сценария выполнения

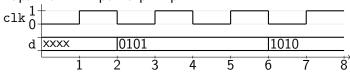

- 9. Последовательный регистр ширины 4

10. Последовательный регистр ширины 4 с синхронным сбросом

- Разработать модуль с заданным поведением

в поддерживаемом фрагменте синтаксиса языка Verilog

- Выполнить программную симуляцию модуля для заданного сценария выполнения

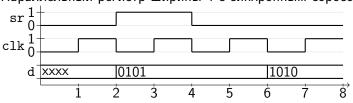

11. Последовательный регистр ширины 4 с асинхронным сбросом

12. Последовательный регистр ширины 4 с включением

- Разработать модуль с заданным поведением

в поддерживаемом фрагменте синтаксиса языка Verilog

- Выполнить программную симуляцию модуля для заданного сценария выполнения

# 13. RS-триггер s 1 r 1 1 2 3 4 5

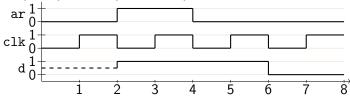

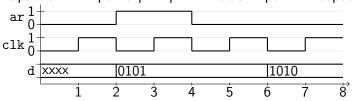

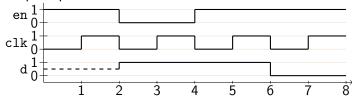

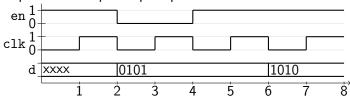

Разработать модуль **синхронной** последовательной схемы с тактовым входом clk, входом асинхронного сброса ar и заданным поведением в поддерживаемом фрагменте языка Verilog:

#### 1. Счётчик чётности

```

вход ширины 1: х выход ширины 1: у:

```

- y(0) = 0

- lacktriangledown если x(t)=0, то y(t+1)=y(t), иначе  $y(t+1)=\overline{y(t)}$

#### 2. Двухбитовый счётчик

выход ширины 2: у:

- lacktriangle порядок следования чисел: 0 o 1 o 2 o 3 o 0

- y(0) = 0

- $\rightarrow$   $y(t) \rightarrow y(t+1)$

Разработать модуль **синхронной** последовательной схемы с тактовым входом clk, входом асинхронного сброса ar и заданным поведением в поддерживаемом фрагменте языка Verilog:

#### 3. Хаотичный двухбитовый счётчик

```

выход ширины 2: у:

```

- lacktriangle порядок следования чисел: 0 o 2 o 3 o 1 o 0

- y(0) = 0

- ightharpoonup y(t)

ightharpoonup y(t+1)

#### 4. Условно-хаотичный двухбитовый счётчик

```

вход ширины 1: х выход ширины 2: у:

```

- y(0) = 0

- lacktriangle если x=0, то y(t) o y(t+1) согласно двухбитовому счётчику

- lacktriangleright если x=1, то y(t) o y(t+1) согласно хаотичному двухбитовому счётчику

Разработать модуль **синхронной** последовательной схемы с тактовым входом clk, входом асинхронного сброса ar и заданным поведением в поддерживаемом фрагменте языка Verilog:

#### 5. Таймер

выход ширины 1: y:  $v(t) = 1 \Leftrightarrow t > 3$

#### 6. Распознаватель 1

вход ширины 1: *х* выход ширины 1: *у*:

▶

$$y(t) = 1 \Leftrightarrow t \geq 4$$

и  $(x(t-3)x(t-2)x(t-1)) = (101)$

#### 7. Распознаватель 2

вход ширины 1: x выход ширины 1: y:

▶

$$y(t) = 1 \Leftrightarrow \exists t' : 4 \leq t' \leq t \text{ in } (x(t'-3)x(t'-2)x(t'-1)) = (101)$$

Разработать модуль **синхронной** последовательной схемы с тактовым входом clk, входом асинхронного сброса ar и заданным поведением в поддерживаемом фрагменте языка Verilog:

8. Делитель частоты 1

выход ширины 1: у:

ightharpoonup y — тактовый сигнал вдвое меньшей частоты по сравнению с clk

9. Делитель частоты 2

выход ширины 1: у:

ightharpoonup y — тактовый сигнал вчетверо меньшей частоты по сравнению с clk

10. Делитель частоты 3

выход ширины 1: у:

ightharpoonup y — тактовый сигнал втрое меньшей частоты по сравнению с clk